DOI: 10.7667/PSPC171799

# 基于 FPGA 和 DSP 的合并单元光数字量校准装置

晁武杰¹, 唐志军¹, 林国栋¹, 翟博龙¹, 黄 彪²

(1. 国网福建省电力有限公司电力科学研究院,福建 福州 350007; 2. 福建亿榕信息技术有限公司,福建 福州 350003)

摘要:高性能的光数字量校准装置有助于提高电子式互感器合并单元的可靠性和高效性。针对电子式互感器合并单元测试的通信报文处理能力和同步性两大难题,提出了基于 FPGA 和 DSP 的光数字量校准装置。分析光数字量校准装置的设计原理和技术难点,研究了基于 FPGA 和 DSP 的设计方案。重点介绍了 FPGA、Blackfin DSP 和人机界面三大功能模块的具体组成,进而深入研究了 FPGA 和 Blackfin DSP 的处理流程。最后将光数字量校准装置与数字化电能测试平台 DRM 进行联合测试,测试结果表明,基于 FPGA 和 DSP 的光数字量校准装置既能满足合并单元测试的功能性需求,又具有较好的实时性。

关键词:光数字;校准;合并单元;电子式互感器

# Optical figure calibration device based on FPGA and DSP for merging unit

CHAO Wujie<sup>1</sup>, TANG Zhijun<sup>1</sup>, LIN Guodong<sup>1</sup>, ZHAI Bolong<sup>1</sup>, HUANG Biao<sup>2</sup> (1. State Grid Fujian Electric Power Research Institute, Fuzhou 350007, China; 2. Fujian Yirong Information Techin, Fuzhou 350003, China)

**Abstract:** High-performance optical digital calibration device helps to improve the reliability and efficiency of electronic transformer combined unit. Aiming at the problem of communication packet processing capability and synchronization of electronic transformer merging unit test, an optical digital calibration device based on FPGA and DSP is designed. The optical digital calibration device design principles and technical difficulties are analyzed. The design scheme based on FPGA and DSP is studied. The concrete components of FPGA, Blackfin DSP and man-machine interface are introduced in detail. And then the processing flow of FPGA and Blackfin DSP is studied in depth. Finally, the optical digital calibration device and the digital power test platform DRM perform joint test. The test results show that the optical digital calibration device based on FPGA and DSP can not only meet the functional requirements of the unit test, but also has good real-time performance.

This work is supported by Science and Technology Project of State Grid Fujian Electric Power Company (No. 521304150043).

Key words: optical figure; calibration; merging unit; electronic transformer

# 0 引言

作为智能变电站的基础元件,合并单元对互感 器传输过来的电气量进行合并和同步处理,并将处 理后的数字信号,以广播的形式发送给间隔层的智 能电子设备实现信息共享。

由于合并单元的重要性,电气研发机构和设备

基金项目: 国网福建省电力有限公司科技项目资助 (521304150043)

厂家陆续研发了各种高性能的合并单元[1]。但相较于合并单元的研发,目前对合并单元测试系统的研究则相对滞后<sup>[2]</sup>。由于缺乏有效的合并单元校准系统,难以对当前各大厂家生产的合并单元进行客观、统一、可信的评判,以促进合并单元生产的规范化;同时合并单元在生产投运、运行维护等阶段都需要进行测试检修,只有依靠有效的校验手段,才能发现合并单元性能的变化,及时发现合并单元潜在的性能下降隐患<sup>[3]</sup>。

合并单元校验系统, 作为衡量合并单元性能的

度量"尺子",需要能够与被测的合并单元形成一个可互动的闭环环节,合并单元校验系统能够向合并单元发送符合其标准的输出量,及时接收从合并单元反馈的信息,并实时记录、处理和评判合并单元信息的准确性。

# 1 光数字量校准

随着合并单元应用的日益增多,电力学界和工业界对合并单元校验系统的研究也日益深入。现阶段的智能变电站的合并单元,主要有电子式互感器或传统电磁式互感器两种类型,电子式互感器通常以光纤通信形式输出数字信号,而传统电磁式互感器则主要输出模拟信号<sup>[4]</sup>。当期合并单元的校验研究多集中于传统电磁式互感器类型。

文献[5]以传统电磁式互感器为研究对象,针对 变电站合并单元测试设备技术性能中"延时特性" 和"准确度"两项关键的测试功能指标缺乏有效校 验手段的问题,提出了一种针对变电站合并单元测 试设备技术性能的校验方法。文献[6]从配置文件测 试、与保护测控设备接口测试、与电子式互感器接 口测试和同步功能测试四个方面介绍了合并单元测 试的内容和方案, 但缺乏对合并单元具体测试技术 的深入研究。文献[7]从信号流程角度,分析模拟量 输入合并单元计量性能测试, 文中侧重于模拟量输 入合并单元的误差环节,并不涉及具体的合并单元 测试系统研究。文献[8]提出了基于 RTDS 的合并单 元测试系统, 在实时数字仿真系统中利用 GTNET-SV 及 GTNET-GSE 模型搭建了合并单元 闭环试验系统, 该系统需要用到价格昂贵的国外仿 真系统 RTDS。

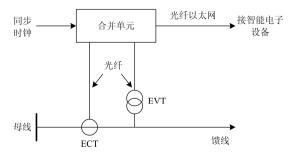

传统电磁式互感器合并单元测试系统涉及模拟量转换,而电子式互感器合并单元通过光纤网络,直接接收来自于ECT和EVT的电流和电压信号<sup>[9-10]</sup>。如图 1 所示,电子式互感器合并单元着重于光纤通信网络和 IEC61850 协议报文的处理,电子式互感器合并单元校验侧重于光数字量的处理。

图 1 电子式互感器合并单元功能

Fig. 1 Merging unit function of electronic transformer

应用于电子式互感器合并单元的光数字量校验装置需要具备强大的网络和协议处理能力,能够满足合并单元测试所需的功能。合并单元基本功能包括:1)时钟同步功能;2)通过光纤网络接收来自于电子式互感器的采集数据,并进行校验、处理功能。3)将各路采样值数据,按照 IEC61850 协议组帧,并通过通信网络发送给到间隔层的智能电子设备[11]。

应用于电子式互感器合并单元的光数字量校验装置,作为合并单元的衡量"尺子",需要能够产生电子式互感器合并单元所需的信号,并接收、记录和分析来自于电子式互感器合并单元信号。光数字量校验装置主要的功能包括<sup>[12]</sup>: 1)接收外部同步信号并输出时钟; 2)通信网络接口; 3)报文记录、统计和分析功能; 4)人机界面和配置等。

### 2 整体设计

应用于电子式互感器合并单元的光数字量校验装置,主要涉及时钟同步信号处理和以通信网络形式传递的数字量电流、电压信息。光数字量校验装置设计难点主要涉及:1)丰富的通信网络接口和高效的电力协议处理能力;2)准确、及时的时间同步处理能力。

由于网络通信的报文到达具有时间上不确定性和时序上并发性等不可控特征,这就要求光数字量校验装置具有强大的并发处理能力,能够同时处理多个通信接口的报文,不出现由于控制器报文处理不及时而出现报文丢失情况。同时,时间同步信号也需要及时处理,并且时间同步信号也可能与网络报文同时到达光数字量校验装置,更需要光数字量校验装置具有能够并发处理不同类型信号的能力<sup>[13]</sup>。

由于合并单元校验系统实现的功能较为复杂,而且对实时处理能力要求很高,一般的处理器不容易同时完成上述功能。因此,本文将基于 FPGA 和 DSP,研发新一代合并单元校验系统。

该光数字量校验装置充分利用 FPGA 强大的并发处理能力和 DSP 在数据处理能力的优势。采用 FPGA 作为主控制器<sup>[14]</sup>,完成需要实时处理的时间同步信号功能,并通过以太网接口与各个辅助的 DSP 交互,同时完成人机界面和配置等功能。

DSP 具有数据处理优势,用以扩展通信网络接口,完成通信网络报文处理和记录能力。考虑到当前合并单元通信基本上采用以太网通信<sup>[15]</sup>, DSP 采用扩展以太网,作为光数字量校验装置的网络接口与合并单元实现闭合测试。

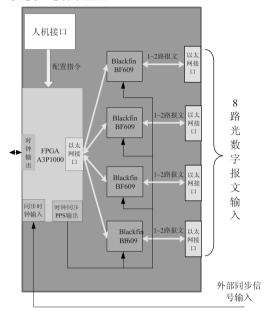

电子式互感器合并单元的光数字量校验装置如图 2 所示,主要由 FPGA 模块、Blackfin DSP 模块和人机接口模块组成。

图 2 光数字量校准装置的内部设计原理图

Fig. 2 Internal design principle of optical digital calibration device

FPGA 模块作为主功能模块,完成时外部同步信号的转换、报文转发测试结果和配置控制命令等功能; Blackfin DSP 模块具有良好的可扩展性,实现光数字量校验装置所需的丰富以太网接口,并完成数字量报文的记录和处理功能; 人机接口模块完成人机交互功能,完成对 FPGA 的配置。

# 3 功能模块

# 3.1 FPGA 模块

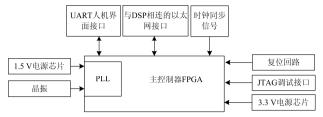

FPGA 模块采用 Actel 公司第三代的 ProASIC3,作为一种安全、高效、低功耗的单芯片控制器解决方案,ProASIC3 提供了 1 kbit 的片内可编程、非挥发性 FlashROM. ProASIC3 芯片有高达 1 M的系统逻辑门和 144 kbits 的双端口 SRAM。而且ProASIC3 芯片自身支持 ARM7 软核,可以配置成ARM7 功能,实现控制器的管理功能;同时,ProASIC3 还可以提供 AES 网络报文加密等安全功能,能方便地满足电力安全报文要求。ProASIC3 I/O管脚提供 LVPECL、LVDS、BLVDS 和 M-LVDS 等差分功能,容易发展为以太网接口。

FPGA 模块设计如图 3 所示,电源芯片将 5 V 电压转换成 1.5 V 和晶振一起提供给 FPGA 的 PLL 环节,同时提供 3.3 V 电压给 FPGA 外围功能模块,并配置复位芯片和 JTAG 调试模块。

图 3 光数字量校准装置的 FPGA 设计

Fig. 3 FPGA design of optical optical calibration device

FPGA 实现的功能如图 3 所示。FPGA 首先实现时钟同步功能,将外部输入同步信号转换成 PPS,并提供给光数字量校验装置的 Blackfin DSP 模块和外部时钟输出。FPGA 配置 UART 串口功能,与人机接口控制器互连,接收来自于人机界面的配置信息。FPGA 实现以太网接口功能,通过以太网连接所有的 Blackfin DSP,实现来自于合并单元的报文记录和处理。

#### 3.2 Blackfin DSP 模块

Blackfin 处理器基于由 ADI 和 Intel 公司联合 开发的微信号架构(MSA),它将一个 32 位 RISC 型指令集和双 16 位乘法累加(MAC)信号处理功能与通用型微控制器所具有的易用性组合在了一起。这种处理特征的组合使得 Blackfin 处理器能够在信号处理和控制处理应用中均发挥上佳的作用,在许多场合中免除了增设单独的异类处理器的需要,简化了硬件和软件设计实现任务。

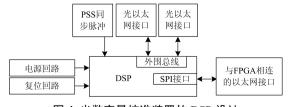

Blackfin DSP 模块主要完成来自于合并单元的报文收发和处理功能,如图 4 所示。时间的同步性对于光数字量校验装置至关重要,Blackfin DSP 模块接收来自于 FPGA 的同步时钟信号,并根据 PPS 进行自身时钟调整,与外部时钟同步。

Blackfin DSP 模块扩展以太网功能,通过多路以太网接口实时接收外部输入的光以太网数据,每接收一帧以太网数据,其内部 MAC 硬件将产生一个外部脉冲,Blackfin DSP 模块捕获此脉冲并添加硬件时戳,此时的时戳即是报文的接收时刻。Blackfin DSP 模块将外部输入的光以太网数据处理后,通过光数字量校验装置的内部以太网,与主控制器 FPGA 模块交互信息。

图 4 光数字量校准装置的 DSP 设计

Fig. 4 DSP design of optical optical calibration device

#### 3.3 人机接口模块

由于主控制器 FPGA 模块专长于具有固定处理 模式的任务并发处理功能,但对于多样化的人接交 互任务则处理相对单薄,因此,增加专门的控制器 进行人机界面处理。

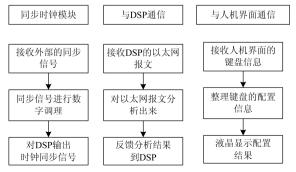

人机界面接口模块负责光数字量校验装置的配置功能,如图 5 所示,实现键盘信息输入和液晶界面显示功能,接收光数字量校验装置的配置信息,并将该信息通过控制器自带的 UART 通信串口传递给主控制器 FPGA 模块。

图 5 光数字量校准装置的人机界面设计

Fig. 5 Man-machine interface design of optical optical calibration device

# 4 处理流程

主控制器 FPGA 采用主流的 Verilog 硬件语言进行编程,通过 Verilog 硬件语言把 FPGA 所需完成的功能描述出来,然后下载到 FPGA 完成所需的功能。 FPGA 模块主要完成时钟管理、与 Blackfin DSP 以太网通信和通过串口通信实现人机管理配置三大功能。

区别于以软件形式串行逐条执行命令的控制器处理方法,FPGA以逻辑门的硬件方式,可以同时完成上述功能,如图 6 所示。时钟管理方面,FPGA接收外部的同步信号,同步信号经数字调理后,进一步生成时钟同步信号提供给 Blackfin DSP 模块,使得光数字量校验装置的 Blackfin DSP 具有统一的同步时钟信号;同时提供时钟输出到外部的合并单元等测试对象。

与 Blackfin DSP 以太网通信是 FPGA 的核心内容,接收来自于 Blackfin DSP 带有时间标签的预处

图 6 FPGA 处理流程

Fig. 6 FPGA processing flow

理报文,对报文进行统计分析,并做出对应的处理后,通过以太网接口将处理结果发送给对应的Blackfin DSP。

串口通信实现人机管理配置功能则相对简单, 接收来自于人机管理控制器的串口请求命令,做出 对应的响应后,根据人机管理控制器的配置信息, 更新光数字量校验装置的参数设置。

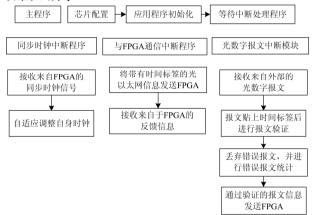

Blackfin DSP 基于 C语言,采用主程序循环加中断处理的软件模式开发。主程序较为简单,完成Blackfin DSP 的芯片配置和应用程序的初始化后,进入中断处理程序。中断处理可以更及时地响应所需完成的任务,为光数字量校验装置 Blackfin DSP模块的关键,分为同步时钟中断模块、与 FPGA 交换中断模块和光数字报文中断模块三个核心环节,如图 7 所示。

图 7 Blackfin DSP 处理流程 Fig. 7 Blackfin DSP processing flow

一旦从 FPGA 发出的同步时钟输出到达 Blackfin DSP 的外部中断管脚,则 Blackfin DSP 进入时钟中断模块处理。时钟中断模块处理程序根据 FPGA 所提供的外部同步时钟,自适应调整自身同步时钟的计算器,以保持整个光数字量校验装置所有元件保持同步。

外部光数字报文到达 Blackfin DSP,则进入光数字报文中断模块。光数字报文中断模块首先给所接收的光数字报文贴上时间标签,进而验证报文的正确性,丢弃有误的报文并进行相关的错误统计,进而将统计信息发送给 FPGA;对于通过验证的报文,对报文进行预处理,并将相关信息发送给 FPGA做进一步分析。

与 FPGA 通信中断模块,主要完成 Blackfin DSP 与 FPGA 的信息交互,包括 Blackfin DSP 将所接收的带有时间标签的光数字报文信息传送给 FPGA,并接收来自于主控制器 FPGA 的反馈信息。

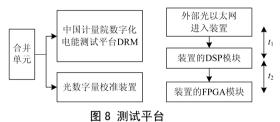

# 5 测试

为了测试本文所研发的光数字量校准装置的性能,搭建如图8的测试平台。合并单元将 DL/T 860.91 或 DL/T 860.92 数字采样值报文,同时输送给到光数字量校准装置和中国计量院数字化电能测试平台 DRM。

光数字量校准装置与 DRM 分别对输入数字采样值报文进行电参数计算,通过对比光数字量校准装置和中国计量院数字化电能测试平台 DRM 的计算结果做校准。

Fig. 8 Testing platform

首先进行光数字量校准装置的功能性测试,验证光数字量校准装置处理合并单元所发出报文的正确性。测试过程中,合并单元在不同的时间点,分别发出符合和不符合 DL/T 860.91 或 DL/T 860.92 的数字采样值报文<sup>[16]</sup>,光数字量校准装置都能准确地识别出报文的正误。

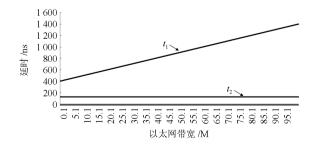

通过实测报文处理的延时性,进一步测试光数字量校准装置的报文实时处理性能。分别设置延时指标  $t_1$  和  $t_2$ ,  $t_1$  表示合并单元发给光数字量校准装置的报文从进入装置到 DSP 处理报文的延时,表征 DSP 模块的处理能力;  $t_2$ 表示 DSP 发出所处理的报文信息到 FPGA 处理该信息的延时,表征 FPGA 模块的处理能力。

报文延时性的测试过程中,合并单元发出的报文频率逐步增加百兆<sup>[17]</sup>,分别记录  $t_1$  和  $t_2$ ,如图 9 所示。

图 9 DSP 和 FPGA 延时测试结果 Fig. 9 DSP and FPGA delay test results

由图 9 可知,表征 DSP 处理能力的  $t_1$  延时较大,而且随着合并单元发出的报文逐步增加而占据网络带宽, $t_1$  延时增加明显,这是由于 DSP 采用串行运行程序方式,执行光数字报文中断模块;随着光数字报文的增加,所需处理的报文需要更多的时间, $t_1$  延时也对应增加。

FPGA 以硬件并行的方式处理 DSP 发送过来的报文, $t_2$  延时较小而且基本固定,该延时主要取决于 FPGA 的器件延时以及功能实现所需的逻辑门规模。

#### 6 结语

区别于电磁式互感器合并单元侧重于电气量的精度,电子式互感器合并单元测试系统需要具有强大的通信报文处理能力和同步性。本文设计了基于FPGA和DSP的光数字量校准装置,用以测试电子式互感器合并单元。介绍光数字量校准装置的设计原理基础上,重点研究了FPGA、Blackfin DSP和人机界面三大功能模块的具体组成,以及FPGA和Blackfin DSP的处理流程。测试结果表明,本文所研发的光数字量校准装置在满足合并单元测试的功能性需求基础上,具有较好的实时性。

# 参考文献

- [1] 赵应兵,周水斌,马朝阳.基于 IEC 61850-9-2 的电子 式互感器合并单元的研制[J]. 电力系统保护与控制, 2010, 38(6): 105-108.

- ZHAO Yingbing, ZHOU Shuibin, MA Chaoyang. Research and manufacture of merging unit based on IEC 61850-9-2[J]. Power System Protection and Control, 2010, 38(6): 105-108.

- [2] 浮明军, 刘昊昱, 董磊超. 智能变电站继电保护装置自动测试系统研究和应用[J]. 电力系统保护与控制, 2015, 43(1): 40-44.

- FU Mingjun, LIU Haoyu, DONG Leichao. Research and application of relay protection automatic test system for smart substation [J]. Power System Protection and Control, 2015, 43(1): 40-44.

- [3] 梅德冬, 樊瑞, 周斌. IEC 61850 模型信息的规则表达与校验研究[J]. 电力系统保护与控制, 2015, 43(3): 131-136.

- MEI Dedong, FAN Rui, ZHOU Bin. Research on regular expressions and check of IEC 61850 model information[J]. Power System Protection and Control, 2015, 43(3): 131-136.

- [4] 樊陈, 倪益民, 耿明志, 等. 智能变电站合并单元技术 规范修订解读[J]. 电力系统自动化, 2016, 40(20): 1-5.

- FAN Chen, NI Yimin, GENG Mingzhi, et al. Interpretation of technical specification revision of merging unit in smart substation[J]. Automation of Electric Power Systems, 2016, 40(20): 1-5.

- [5] 欧阳帆,朱维钧,陈宏,等.变电站合并单元测试设备校验系统及其实现[J].电力系统自动化,2017,41(18):1-7.

- OUYANG Fan, ZHU Weijun, CHEN Hong, et al. Calibration system for substation merging unit test equipment and its implementation[J]. Automation of Electric Power Systems, 2017, 41(18): 1-7.

- [6] 殷志良, 李敏, 袁成, 等. 数字化变电站合并单元的应用和测试[J]. 供用电, 2011, 28(5): 37-39.

YIN Zhiliang, LI Min, YUAN Cheng, et al. Application and testing of merging unit for digital substation[J]. Distribution & Utilization, 2011, 28(5): 37-39.

- [7] 王忠东,李红斌,程含渺,等.模拟量输入合并单元计量性能测试研究[J]. 电网技术,2014,38(12):3522-3527.

- WANG Zhongdong, LI Hongbin, CHENG Hanmiao, et al. Analog-input merging unit digital electric energy metering system testing of metering performance testing specification[J]. Power System Technology, 2014, 38(12): 3522-3527.

- [8] 李罗, 朱静, 白云飞, 等. 基于 RTDS 的合并单元性 能测试研究[J]. 高压电器, 2014, 50(7): 24-30. LI Luo, ZHU Jing, BAI Yunfei, et al. Research on performance test of merging unit based on RTDS[J].

High Voltage Apparatus, 2014, 50(7): 24-30.

- [9] 蔡骥然,郑永康,周振宇,等.智能变电站二次设备状态监测研究综述[J]. 电力系统保护与控制,2016,44(6):148-154.

- CAI Jiran, ZHENG Yongkang, ZHOU Zhenyu, et al. A survey of research on secondary device condition monitoring in smart substation[J]. Power System Protection and Control, 2016, 44(6): 148-154.

- [10] 李妍, 车勇, 单强, 等. 智能变电站二次系统在线监测评估的研究[J]. 电力系统保护与控制, 2016, 44(10): 65-70.

- LI Yan, CHE Yong, SHAN Qiang, et al. Research on secondary system on-line monitoring and evaluation in smart substation[J]. Power System Protection and Control, 2016, 44(10): 65-70.

- [11] 温东旭, 杨辉, 王旭宁, 等. 电力保护装置保障性自动测试方案研究与实践[J]. 电力系统保护与控制, 2015, 43(10): 135-138.

- WEN Dongxu, YANG Hui, WANG Xuning, et al. Research

- and practice on the scheme of automatic testing of power protection device security[J]. Power System Protection and Control, 2015, 43(10): 135-138.

- [12] 陈德辉, 王丰, 杨志宏. 智能变电站二次系统通用测试平台方案[J]. 电力系统保护与控制, 2016, 44(1): 139-143

- CHEN Dehui, WANG Feng, YANG Zhihong. Unified test platform for smart substation secondary system [J]. Power System Protection and Control, 2016, 44(1): 139-143.

- [13] 鲍伟, 高翔, 沈冰, 等. 智能变电站非侵入测试技术研究[J]. 电力系统保护与控制, 2015, 43(20): 125-129. BAO Wei, GAO Xiang, SHEN Bing, et al. Research method of "non-intruding test" for smart substation[J]. Power System Protection and Control, 2015, 43(20): 125-129.

- [14] 王成山, 丁承第, 李鹏, 等. 基于 FPGA 的配电网暂 态实时仿真研究(一): 功能模块实现[J]. 中国电机工程学报, 2014, 34(1): 161-167.

- WANG Chengshan, DING Chengdi, LI Peng, et al. Real-time transient simulation for distribution systems based on FPGA, part I: module realization[J]. Proceedings of the CSEE, 2014, 34(1): 161-167.

- [15] 智能变电站技术导则: Q/GDW 383—2009[S]. 北京: 国家电网公司, 2009.

- [16] Communication networks and systems for power utility automation: part 6 configuration description language for communication in electrical substations related to IEDs: IEC 61850-6[S]. 2008.

- [17] 王智东, 王钢, 许志恒, 等. 一种改进的 GOOSE 报文 HMAC 认证方法(英文)[J]. 电网技术, 2015, 39(12): 3627-3634.

- WANG Zhidong, WANG Gang, XU Zhiheng, et al. An HMAC based authenticated method for GOOSE packets[J]. Power System Technology, 2015, 39(12): 3627-3634.

# 收稿日期: 2017-12-11; 修回日期: 2018-01-25 作者简介:

晁武杰(1983—), 男, 博士, 工程师, 主要研究方向为智能变电站继电保护技术; E-mail: zlwng2016@163.com

唐志军(1973—),男,硕士,高工,主要研究方向为电力系统继电保护与自动化;

林国栋(1974—),男,本科,高工,主要研究方向为电力系统继电保护与自动化技术。

(编辑 张爱琴)